SDRAM

SDRAM (англ. Synchronous Dynamic Random Access Memory — синхронная динамическая память с произвольным доступом) — тип запоминающего устройства, использующегося в компьютере и других цифровых устройствах в качестве ОЗУ.

В отличие от других типов DRAM, использовавших асинхронный обмен данными, ответ на поступивший в устройство управляющий сигнал возвращается не сразу, а лишь при получении следующего тактового сигнала. Тактовые сигналы позволяют организовать работу SDRAM в виде конечного автомата, исполняющего входящие команды. При этом входящие команды могут поступать в виде непрерывного потока, не дожидаясь, пока будет завершено выполнение предыдущих инструкций (конвейерная обработка): сразу после команды записи может поступить следующая команда, не ожидая, когда данные окажутся записаны. Поступление команды чтения приведёт к тому, что на выходе данные появятся спустя некоторое количество тактов — это время называется задержкой и является одной из важных характеристик данного типа устройств.

Циклы обновления выполняются сразу для целой строки, в отличие от предыдущих типов DRAM, обновлявших данные по внутреннему счётчику, используя способ обновления по команде CAS перед RAS.

История использования

[править | править код]Массовый выпуск SDRAM начался в 1997 году. Первоначально этот тип памяти предлагался в качестве альтернативы для дорогой видеопамяти (VRAM), однако вскоре SDRAM завоевал популярность и стал применяться в качестве ОЗУ, постепенно вытесняя другие типы динамической памяти. Последовавшие затем технологии DDR позволили сделать SDRAM ещё эффективнее. За разработкой DDR SDRAM последовали стандарты DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM и DDR5 SDRAM.

SDR SDRAM

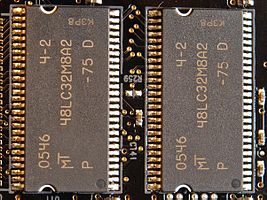

[править | править код]Первый стандарт SDRAM с появлением последующих стандартов стал именоваться SDR (Single Data Rate — в отличие от Double Data Rate). За один такт принималась одна управляющая команда и передавалось одно слово данных. Типичными тактовыми частотами были 66, 100 и 133 МГц. Микросхемы SDRAM выпускались с шинами данных различной ширины (обычно 4, 8 или 16 бит), но как правило, эти микросхемы входили в состав 168-контактного модуля DIMM, который позволял прочитать или записать 64 бита (в варианте без контроля чётности) или 72 бита (с контролем чётности) за один такт.

Использование шины данных в SDRAM оказалось осложнено задержкой в 2 или 3 такта между подачей сигнала чтения и появлением данных на шине данных, тогда как во время записи никакой задержки быть не должно. Потребовалась разработка достаточно сложного контроллера, который не позволял бы использовать шину данных для записи и для чтения в один и тот же момент времени.

Управляющие сигналы

[править | править код]Команды, управляющие модулем памяти SDR SDRAM, подаются на контакты модуля по 7 сигнальным линиям. По одной из них подается тактовый сигнал, передние (нарастающие) фронты которого задают моменты времени, в которые считываются команды управления с остальных 6 командных линий. Имена (в скобках — расшифровки имен) шести командных линий и описания команд приведены ниже:

- CKE (англ. clock enable, разрешение тактового сигнала) — при низком уровне сигнала блокируется подача тактового сигнала на микросхему. Команды не обрабатываются, состояние других командных линий игнорируется.

- /CS (англ. chip select, выбор ИС) — при высоком уровне сигнала все прочие управляющие линии, кроме CKE, игнорируются. Действует как команда NOP (нет оператора).

- DQM (англ. data mask, маска данных) — высокий уровень на этой линии запрещает чтение/запись данных. При одновременно поданной команде записи данные не записываются в DRAM. Присутствие этого сигнала в двух тактах, предшествующих циклу чтения, приводит к тому, что данные не считываются из памяти.

- /RAS (англ. row address strobe, строб адреса строки) — несмотря на название, это не строб, а всего лишь один командный бит. Вместе с /CAS и /WE кодирует одну из 8 команд.

- /CAS (англ. column address strobe, строб адреса столбца) — несмотря на название, это не строб, а всего лишь один командный бит. Вместе с /RAS и /WE кодирует одну из 8 команд.

- /WE (англ. write enable, разрешение записи) — вместе с /RAS и /CAS кодирует одну из 8 команд.

Устройства SDRAM внутренне разделены на 2 или 4 независимых банка памяти. Входы адреса первого и второго банка памяти (BA0 и BA1) определяют, какому банку предназначена текущая команда.

Принимаются следующие команды:

| /CS | /RAS | /CAS | /WE | BAn | A10 | An | Команда |

|---|---|---|---|---|---|---|---|

| В | x | x | x | x | x | x | задержка команды (нет операции) |

| Н | В | В | В | x | x | x | нет операции |

| Н | В | В | Н | x | x | x | остановить текущую операцию пакетного чтения или записи. |

| Н | В | Н | В | № банка | Н | № столбца | считать пакет данных из активного в данный момент ряда. |

| Н | В | Н | В | № банка | В | № столбца | как и предыдущая команда, а по завершении команды регенерировать и закрыть этот ряд. |

| Н | В | Н | Н | № банка | Н | № столбца | записать пакет данных в активный в данный момент ряд. |

| Н | В | Н | Н | № банка | В | № столбца | как и предыдущая команда, а по завершении команды регенерировать и закрыть этот ряд. |

| Н | Н | В | В | № банка | № ряда | открыть ряд для операций записи и чтения. | |

| Н | Н | В | Н | № банка | Н | x | деактивировать текущий ряд выбранного банка. |

| Н | Н | В | Н | x | В | x | деактивировать текущий ряд всех банков. |

| Н | Н | Н | В | x | x | x | регенерировать по одному ряду каждого из банков, используя внутренний счётчик. Все банки должны быть деактивированы. |

| Н | Н | Н | Н | 0 0 | РЕЖИМ | с линий A0—A9 загрузить в микросхему параметры конфигурирования. Наиболее важные — CAS latency (2 или 3 такта) и длина пакета (1, 2, 4 или 8 тактов) | |

Примеры

[править | править код]Ссылки

[править | править код]- iXBT: FAQ по SDRAM Архивная копия от 11 октября 2007 на Wayback Machine

Для улучшения этой статьи желательно:

|